loading...

UVM course helps engineers to develop UVM testbench environment with efficient testcase development. In UVM environment, you will be developing stimulus Sequencer, Driver, Monitor, Scoreboard and Coverage. Our industry experienced instructor will train you:

Course Duration : 30hrs

Batch type:

Course Duration : 45hrs

Our industry experienced instructor will train you:

Course Duration : 30hrs

Batch type:

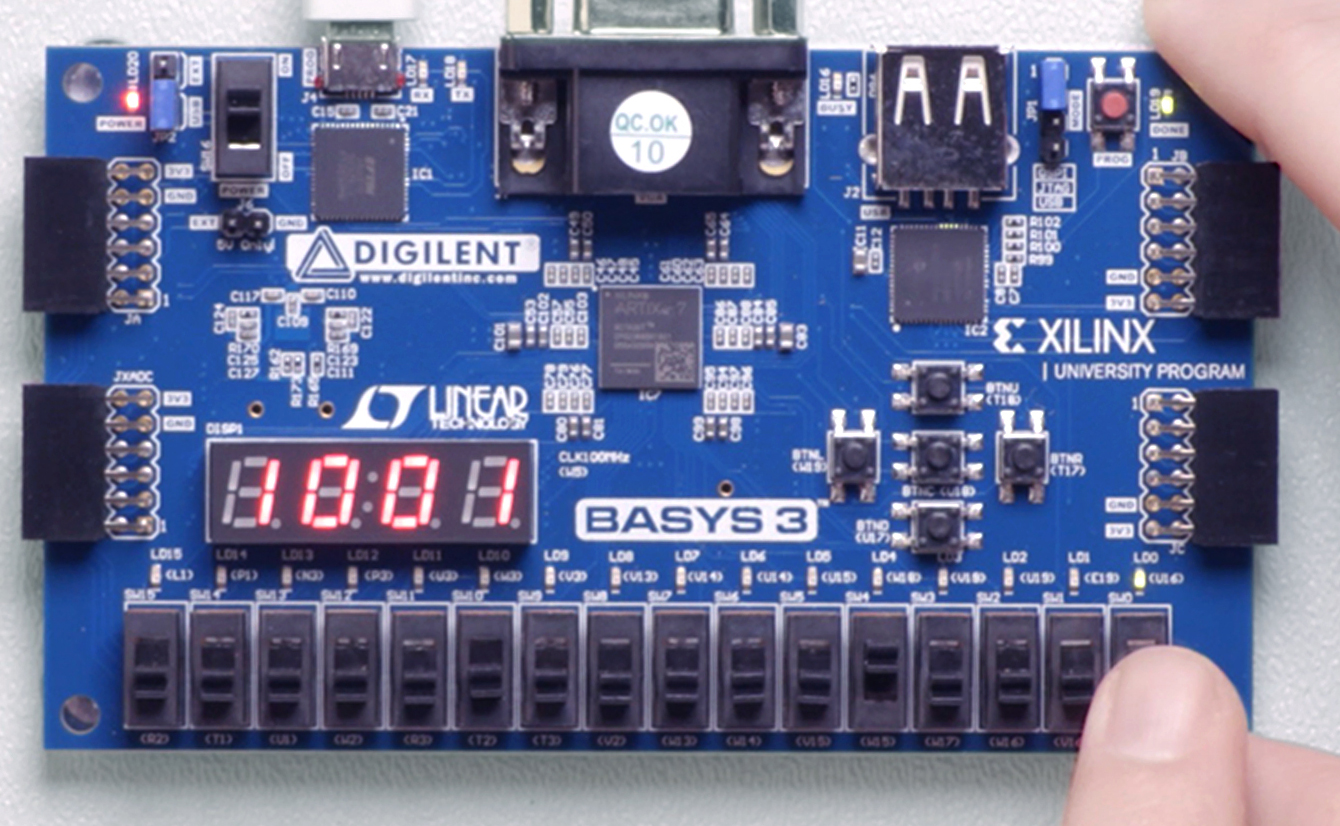

VHDL is another hardware description language which is used to model digital systems. Learn the fundamental skills for programming in VHDL, specifically for modeling and designing digital circuits and systems. The course includes both behavioral and structural coding techniques, as well as examples of memory, finite state machines and datapath units. The synthesis of designs is also examined. Our industry experienced instructor will train you:

Course Duration : 30hrs

Batch type:

Course Duration : 9 weeks

Digital Design is one of the must have course to VLSI engineers. As a RTL design engineer, the final aim is to build the optimized digital system in terms of speed, power and area that would not be possible without having thorough understanding of digital hardware.

Digital Design course gives you a complete insight into the design of digital system fundamentals from a practical point of view. Our interest mainly focuses more on the system level design rather than circuit level.Our Digital Design course takes you from basic digital design to advanced level. Our industry experienced instructor will train you:

Course Duration : 30hrs

Digital Design course is recommended for graduates/post graduates who wish to enter in the world of digital VLSI.

There are no pre-requisites for learning digital design but having knowledge of basic electronics would be beneficial.

Batch type: