loading...

In the field of VLSI (Very Large-Scale Integration) design, System Verilog has emerged as a powerful hardware description and verification language. With its rich features and versatility, System Verilog has become the go-to choice for designers and verification engineers. System Verilog is a hardware description and verification language that has become widely adopted in the field of VLSI design. It is an extension of the original Verilog language, offering additional features and enhancements to support system-level modeling, design, and verification.

System Verilog combines the power of traditional hardware description with modern programming constructs, such as object-oriented programming and assertions, making it a versatile language for designing and verifying complex digital circuits. With its ability to describe both the structure and behavior of a design, System Verilog enables designers to create reusable and modular code, facilitating efficient development and verification of VLSI designs. Let us explore the power of System Verilog and provide a comprehensive guide for aspiring designers who seek to unlock its potential.

Understanding System Verilog:

System Verilog is an extension of the Verilog hardware description language, designed specifically for system-level modeling, design, and verification. It offers a wide range of features that enhance the expressiveness, productivity, and reusability of hardware designs.

a. Object-Oriented Programming (OOP) Capabilities:

System Verilog introduces OOP features like classes, inheritance, and polymorphism. These features enable designers to create reusable and modular code, improving productivity and design efficiency.

b. Assertion-Based Verification (ABV):

System Verilog provides a built-in assertion language that allows designers to specify properties and constraints on the design. These assertions help in formal verification, functional coverage, and debugging, ensuring the correctness of the design.

c. Functional Coverage:

System Verilog introduces constructs for functional coverage modeling. By defining coverage points, designers can track the completeness of test scenarios, ensuring that all design functionality is exercised during verification.

Designing with System Verilog:

a. RTL Design:

System Verilog supports Register Transfer Level (RTL) design, allowing designers to describe digital circuits using high-level abstractions. It provides features like data types, operators, control flow constructs, and procedural blocks, enabling concise and readable RTL code.

b. OOP-Based Design:

Using classes and inheritance, designers can create reusable and hierarchical design structures in System Verilog. This promotes modularity, code reusability, and scalability, facilitating the development of complex designs.

c. Design Verification:

System Verilog facilitates design verification by enabling designers to write testbenches and test scenarios. With the built-in ABV constructs, designers can define assertions, checkers, and coverage models to ensure functional correctness and comprehensive verification.

Verification with System Verilog:

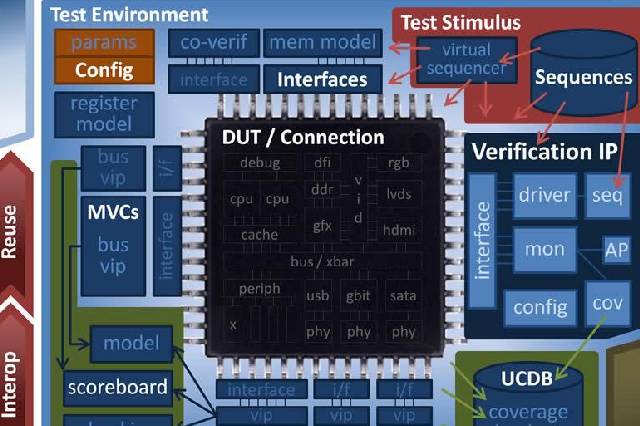

a. Testbench Architecture:

System Verilog offers a powerful testbench architecture called the Universal Verification Methodology (UVM). UVM provides a standardized methodology for building reusable, scalable, and modular testbenches. It simplifies the creation of self-checking testbenches and promotes efficient and organized verification practices.

b. Assertions and Functional Coverage:

System Verilog's assertion language and functional coverage constructs play a crucial role in verification. Designers can write assertions to check properties and constraints during simulation, facilitating bug detection and reducing debug time. Functional coverage models help ensure that all aspects of the design have been tested, leading to comprehensive verification.

c. Simulation and Debugging:

System Verilog provides a rich set of simulation and debugging features. It supports advanced simulation techniques like constrained random testing, coverage-driven verification, and transaction-level modeling. Designers can also leverage waveform viewers and debuggers to analyze and debug complex designs.

Resources and Learning:

a. Online Resources:

Numerous online resources, tutorials, and forums provide valuable insights into System Verilog. Websites like EDA Playground, SystemVerilog.io, and Stack Overflow offer code examples, discussions, and learning materials to help designers deepen their understanding and expand their skills.

b. Training Programs:

Enrolling in professional training programs or courses that focus on System Verilog can accelerate the learning process. These programs provide structured learning materials, hands-on exercises, and expert guidance, equipping designers with practical skills and real-world experience.

System Verilog is a powerful language that empowers designers and verification engineers to develop complex VLSI designs with confidence. Its rich features, including OOP capabilities, assertion-based verification, and functional coverage, make it a versatile language for both design and verification. By exploring the comprehensive guide outlined in this blog, aspiring designers can unleash the full potential of System Verilog and embark on a successful journey in the field of VLSI design.

Are you ready to demystify System Verilog and unleash its power in your designs? FutureWiz Academy offers a comprehensive System Verilog hardware description and verification language course that will equip you with the necessary skills and knowledge to excel in this field. Join FutureWiz Academy today and unlock your potential as a VLSI design professional.

Verilog Essentials: Mastering the Fundamentals of Hardware Description Language

Verilog Essentials: Mastering the Fundamentals of Hardware Description Language

Unleashing the Power of System Verilog: A Comprehensive Guide for Aspiring Designers

Unleashing the Power of System Verilog: A Comprehensive Guide for Aspiring Designers

Demystifying VLSI ch Design: Exploring the Core Concepts of VLSI Courses

Demystifying VLSI ch Design: Exploring the Core Concepts of VLSI Courses

Basics of VLSI - An Ultimate Guide

Basics of VLSI - An Ultimate Guide

Career Prospects After Completing A VLSI Course

Career Prospects After Completing A VLSI Course

Top 5 Reasons To Take Up A Professional VLSI Course

Top 5 Reasons To Take Up A Professional VLSI Course

Mastering VLSI Design: A Comprehensive Guide To Understanding Complex Integrated Circuits

Mastering VLSI Design: A Comprehensive Guide To Understanding Complex Integrated Circuits

Future-Proof Your Career With A VLSI Course: How Learning About Integrated Circuits Can Boost Your Job Prospects?

Future-Proof Your Career With A VLSI Course: How Learning About Integrated Circuits Can Boost Your Job Prospects?

System Verilog: An Overview

System Verilog: An Overview

Introduction to Hardware Description Language (HDL)

Introduction to Hardware Description Language (HDL)

Unlock The Potential Of VLSI Design With An Integrated VLSI Course Online

Unlock The Potential Of VLSI Design With An Integrated VLSI Course Online

Universal Verification Methodology:An Efficient Verification Approach

Universal Verification Methodology:An Efficient Verification Approach

How to Write a Verilog Module for Design and Testbench

How to Write a Verilog Module for Design and Testbench

What Are the Different Career Paths in the VLSI Industry?

What Are the Different Career Paths in the VLSI Industry?

Skills required to establish a successful career in VLSI

Skills required to establish a successful career in VLSI Looking for online VLSI courses? Futurewiz can fulfill your upskilling needs!

Looking for online VLSI courses? Futurewiz can fulfill your upskilling needs! The Future Of VLSI- Get All The Latest Insights!

The Future Of VLSI- Get All The Latest Insights! Super 50 Program For Advanced VLSI Design Training

Super 50 Program For Advanced VLSI Design Training Steps to Build Career in VLSI

Steps to Build Career in VLSI Similarities between C and Verilog

Similarities between C and Verilog What is UVM - A High-level overview

What is UVM - A High-level overview