loading...

In the world of digital design, Verilog has become a cornerstone language for describing and simulating electronic systems. As a Hardware Description Language (HDL), Verilog provides engineers with a powerful tool to design, model, and verify complex digital circuits. In this blog, we will delve into the essentials of Verilog, equipping aspiring designers with the fundamental knowledge needed to master this versatile HDL.

Verilog is a hardware description language used to model and design digital circuits. It offers a concise and structured syntax that allows designers to describe the behavior and structure of electronic systems at various levels of abstraction. Verilog supports both structural and behavioral modeling, making it a versatile language for digital design.

a. Modules:

Modules are the basic building blocks of Verilog designs. They encapsulate functionality and can be instantiated multiple times. Modules define input and output ports, internal signals, and the behavior of the circuit.

b. Data Types:

Verilog provides different data types to represent variables and signals. These include wire, reg, integer, real, and more. Understanding and correctly using these data types is essential for modeling and simulation.

c. Operators:

Verilog offers a range of operators, such as arithmetic, bitwise, logical, and relational operators. These operators allow designers to perform various operations on signals and variables within the circuit.

d. Procedural Blocks:

Procedural blocks, such as always and initial blocks, define the behavior of the circuit. They contain procedural statements that describe how the circuit should operate and respond to inputs.

a. Behavioral Modeling:

Behavioral modeling in Verilog focuses on describing the functionality and operation of a circuit using procedural statements. It is ideal for high-level design and algorithmic descriptions. Behavioral models specify how signals change over time based on the input values.

b. Structural Modeling:

Structural modeling involves describing a circuit's structure using hierarchical connections between different modules. It represents the physical interconnection of components and subcircuits. Structural modeling is suitable for lower-level design and allows for easy reuse of modules.

c. Gate-Level Modeling:

Gate-level modeling describes circuits in terms of basic logic gates and their interconnections. It provides a low-level representation of the circuit, which is useful for simulation and synthesis at the gate level.

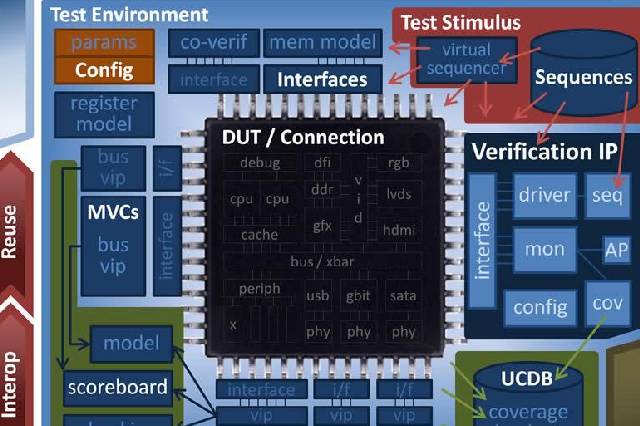

a. Testbench Development:

Verilog allows designers to develop testbenches, which are modules that stimulate the design under test (DUT) with input stimuli and check the correctness of the output responses. Testbenches include test vectors, monitors, and assertions to validate the behavior of the circuit.

b. Simulation:

Simulation is a crucial step in the design process, allowing designers to validate and debug their Verilog designs. Tools like ModelSim, VCS, and QuestaSim facilitate simulation and waveform viewing, enabling designers to analyze the behavior of the circuit and identify any issues.

c. Timing and Functional Verification:

Verilog offers constructs for specifying timing constraints and performing functional verification. Timing verification ensures that the design meets the required performance specifications, while functional verification confirms that the circuit operates correctly under various conditions.

a. Online Tutorials and References:

Numerous online resources, tutorials, and documentation provide detailed explanations and examples of Verilog coding. Websites like Verilog Tutorial and ASIC World offer comprehensive tutorials and code snippets to help designers deepen their understanding of Verilog.

b. Verilog Online Communities and Forums:

Engaging with Verilog online communities and forums can be immensely beneficial for further learning and gaining insights from experienced designers. Websites like Verilog.com and Stack Exchange have active communities where designers can ask questions, participate in discussions, and share knowledge with fellow Verilog enthusiasts. These platforms provide opportunities to collaborate, seek guidance, and stay updated with the latest trends and advancements in Verilog.

Mastering the essentials of Verilog is a fundamental step in becoming a skilled digital design engineer. By understanding Verilog's syntax, building blocks, and modeling techniques, designers can effectively describe, simulate, and verify complex digital circuits. Whether it's behavioral modeling, structural design, or verification, Verilog provides a powerful language to bring digital designs to life.

So, are you ready to embark on your Verilog journey? By mastering the essentials of this hardware description language, you can unlock a world of possibilities and become a proficient digital design engineer. Join FutureWiz Academy and learn the fundamentals of hardware description language.

Verilog Essentials: Mastering the Fundamentals of Hardware Description Language

Verilog Essentials: Mastering the Fundamentals of Hardware Description Language

Unleashing the Power of System Verilog: A Comprehensive Guide for Aspiring Designers

Unleashing the Power of System Verilog: A Comprehensive Guide for Aspiring Designers

Demystifying VLSI ch Design: Exploring the Core Concepts of VLSI Courses

Demystifying VLSI ch Design: Exploring the Core Concepts of VLSI Courses

Basics of VLSI - An Ultimate Guide

Basics of VLSI - An Ultimate Guide

Career Prospects After Completing A VLSI Course

Career Prospects After Completing A VLSI Course

Top 5 Reasons To Take Up A Professional VLSI Course

Top 5 Reasons To Take Up A Professional VLSI Course

Mastering VLSI Design: A Comprehensive Guide To Understanding Complex Integrated Circuits

Mastering VLSI Design: A Comprehensive Guide To Understanding Complex Integrated Circuits

Future-Proof Your Career With A VLSI Course: How Learning About Integrated Circuits Can Boost Your Job Prospects?

Future-Proof Your Career With A VLSI Course: How Learning About Integrated Circuits Can Boost Your Job Prospects?

System Verilog: An Overview

System Verilog: An Overview

Introduction to Hardware Description Language (HDL)

Introduction to Hardware Description Language (HDL)

Unlock The Potential Of VLSI Design With An Integrated VLSI Course Online

Unlock The Potential Of VLSI Design With An Integrated VLSI Course Online

Universal Verification Methodology:An Efficient Verification Approach

Universal Verification Methodology:An Efficient Verification Approach

How to Write a Verilog Module for Design and Testbench

How to Write a Verilog Module for Design and Testbench

What Are the Different Career Paths in the VLSI Industry?

What Are the Different Career Paths in the VLSI Industry?

Skills required to establish a successful career in VLSI

Skills required to establish a successful career in VLSI Looking for online VLSI courses? Futurewiz can fulfill your upskilling needs!

Looking for online VLSI courses? Futurewiz can fulfill your upskilling needs! The Future Of VLSI- Get All The Latest Insights!

The Future Of VLSI- Get All The Latest Insights! Super 50 Program For Advanced VLSI Design Training

Super 50 Program For Advanced VLSI Design Training Steps to Build Career in VLSI

Steps to Build Career in VLSI Similarities between C and Verilog

Similarities between C and Verilog What is UVM - A High-level overview

What is UVM - A High-level overview