loading...

In 2002 eRM (e-Reuse Methodology) from Verisity is introduced that provided rules for building reusable, consistent, extensible and Plug and Play verification environments. In 2003 RVM (Reuse Verification Methodology) from Synopsis for Vera verification language is introduced it included base classes, message capabilities and packing guidelines. In 2006 AVM (Advanced Verification Methodology) from Mentor came and it was first open source Verification solution. Concept of TLM ports were adopted from System C to communicate between Verification Components. In 2007 URM (Universal Reuse Methodology) from Cadence that modified eRM with added features such as factory, configuration and class automation for SV. In 2008 OVM (Open Verification Methodology) from Cadence and Mentor provided multi-vendor verification solution. Integration of multi-language test benches was also added.

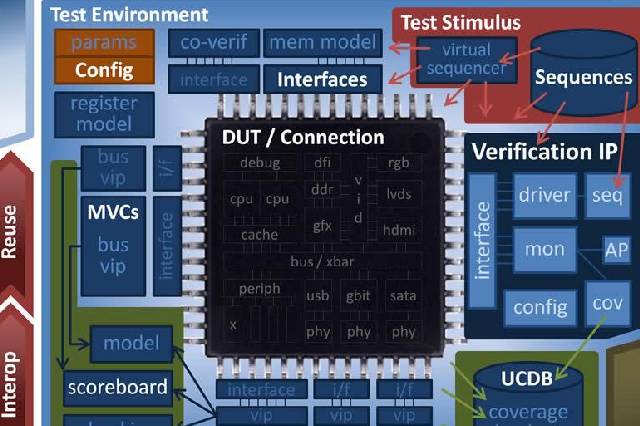

In 2010 UVM (Universal Verification Methodology) from Mentor, Cadence and Synopsis came into picture it is based on OVM, and adopted as a proven library industry wide verification methodology. It is methodology for verification that uses System Verilog or we can say System Verilog is the foundation of UVM. This methodology provides basic building blocks, coding guidelines and advice on reusing verification components. UVM Test Benches are layered and structured test benches, where each structure has a specific role to play

The UVM library provides all the building blocks that we require to build modular, scalable, reusable, verification environments. This library contains base classes, utilities and macros to support the entire verification process.

uvm_void class is the base class for all UVM classes. It is an abstract class with no data members or functions. uvm_object class is the base class for all UVM data and hierarchical classes. uvm_transaction class is base class for all UVM Transaction, It inherits all features of uvm_object. uvm_report_object class provides an interface to UVM reporting facility. It allows UVM Components to issue various messages during simulation time. uvm_component is the base class for all UVM Components. Components are quasi-static objects that exists throughout the simulation In addition it provides Hierarchy, searching and traversing component hierarchy, Phasing, defines test flow of all the components. Configuration, allows configuring component topology. Factory, for creating and overriding components

In System Verilog classes are instantiated at run-time. This raise a questions that what will be the good time to start data generation and transfer, assuming all verification components have been created and connected properly. ? UVM Provides concept of Phases to solve this issue. Each phase has a defined order of execution.

All phases works on bottom up manner (child is connected with parent) except Build phase which works on top down approach. All phases are functions while Run phase which is time consuming is a task and runs in parallel. Run phase is further sub divided into four phases that executes one after other as shown in fig 4.

Components can raise and drop objection (phase.raise_objection (this) , phase.drop_objection (this)). Raising and dropping of objection is done in run phase and a component that raises objection remains in same phase till all the objections are dropped.

Universal Verification Methodology is a standardized methodology for verifying IC and SOC designs. The UVM class library brings much automation to the system Verilog language such as sequences , sequencers , reporting and data automation features etc. This methodology is an Accellera standard with support from multiple vendors: Aldec, Cadence, Mentor Graphics, and Synopsys due to which it is universally acceptable Verification methodology

Verilog Essentials: Mastering the Fundamentals of Hardware Description Language

Verilog Essentials: Mastering the Fundamentals of Hardware Description Language

Unleashing the Power of System Verilog: A Comprehensive Guide for Aspiring Designers

Unleashing the Power of System Verilog: A Comprehensive Guide for Aspiring Designers

Demystifying VLSI ch Design: Exploring the Core Concepts of VLSI Courses

Demystifying VLSI ch Design: Exploring the Core Concepts of VLSI Courses

Basics of VLSI - An Ultimate Guide

Basics of VLSI - An Ultimate Guide

Career Prospects After Completing A VLSI Course

Career Prospects After Completing A VLSI Course

Top 5 Reasons To Take Up A Professional VLSI Course

Top 5 Reasons To Take Up A Professional VLSI Course

Mastering VLSI Design: A Comprehensive Guide To Understanding Complex Integrated Circuits

Mastering VLSI Design: A Comprehensive Guide To Understanding Complex Integrated Circuits

Future-Proof Your Career With A VLSI Course: How Learning About Integrated Circuits Can Boost Your Job Prospects?

Future-Proof Your Career With A VLSI Course: How Learning About Integrated Circuits Can Boost Your Job Prospects?

System Verilog: An Overview

System Verilog: An Overview

Introduction to Hardware Description Language (HDL)

Introduction to Hardware Description Language (HDL)

Unlock The Potential Of VLSI Design With An Integrated VLSI Course Online

Unlock The Potential Of VLSI Design With An Integrated VLSI Course Online

Universal Verification Methodology:An Efficient Verification Approach

Universal Verification Methodology:An Efficient Verification Approach

How to Write a Verilog Module for Design and Testbench

How to Write a Verilog Module for Design and Testbench

What Are the Different Career Paths in the VLSI Industry?

What Are the Different Career Paths in the VLSI Industry?

Skills required to establish a successful career in VLSI

Skills required to establish a successful career in VLSI Looking for online VLSI courses? Futurewiz can fulfill your upskilling needs!

Looking for online VLSI courses? Futurewiz can fulfill your upskilling needs! The Future Of VLSI- Get All The Latest Insights!

The Future Of VLSI- Get All The Latest Insights! Super 50 Program For Advanced VLSI Design Training

Super 50 Program For Advanced VLSI Design Training Steps to Build Career in VLSI

Steps to Build Career in VLSI Similarities between C and Verilog

Similarities between C and Verilog What is UVM - A High-level overview

What is UVM - A High-level overview